# A Wideband Ultra-Low Current Noise Transimpedance Amplifier for Ultrafast Wideband THz Communication

Tanjil Shivan<sup>1</sup>, Maruf Hossain<sup>1</sup>, Ralf Doerner<sup>1</sup>, Hady Yacoub<sup>1</sup>, Bradly Snyder<sup>2</sup>, Zerihun Tegegne<sup>2</sup>, Milan Deumer<sup>3</sup>, Simon Nellen<sup>3</sup>, David de Felipe Mesquida<sup>3</sup>, Wolfgang Heinrich<sup>1</sup> and Viktor Krozer<sup>1,4</sup>

<sup>1</sup>Ferdinand-Braun-Institut (FBH), 12489 Berlin, Germany.

<sup>2</sup>PHIX B.V., 7522 NM Enschede, The Netherlands

<sup>3</sup>Fraunhofer-Institut für Nachrichtentechnik, Heinrich-Hertz-Institut (HHI), 10587, Berlin, Germany

<sup>4</sup>Goethe University of Frankfurt am Main, 60438 Frankfurt am Main, Germany.

Email: <sup>1</sup>tanjil.shivan@fbh-berlin.de

Abstract— This work reports a wideband transimpedance amplifier MMIC with ultra-low input referred noise current. Being based on transferred substrate InP DHBT process, this work achieves a significant leap forward for ultra-low noise transimpedance amplifier design particularly in HBT based processes, in which, low noise characteristic is fundamentally challenging to achieve. Using a low bias current for amplification, the noise current is kept low. As a result, the amplification is achieved without compromising the noise current performance of the circuit. A 3-dB bandwidth from DC to 10 GHz was achieved with a transimpedance gain of beyond 50 dB $\Omega$  with a measured input referred noise current density of 3  $pA/\sqrt{Hz}$ . To the authors best knowledge, this is the lowest reported input-referred noise current density for InP DHBT based TIA, covering such wide bandwidth.

*Keywords*— Transimpedance amplifier (TIA), input referred noise current density.

# I. INTRODUCTION

Ultra-low-noise performance is a crucial factor in determining the maximum data rate for a given optical receiver sensitivity. Low-noise TIA performance can improve the receiver module in either or both data rate and  $T_r/R_r$  distance. The eventual benefit of such a low noise TIA is the possibility of widening the bandwidth for higher data rate applications. Traditionally, the low noise TIA were implemented in SiGe HBT [1], CMOS [2], InP DHBT [3] with SiGe HBT based TIA reaching up to 5.5  $pA/\sqrt{Hz}$  of input referred noise. This is the state-of-the-art in these technologies for TIA circuits. However, combining a TIA with low noise feature together with high linearity is technologically challenging for the aforementioned technologies. InP HBTs, have shown that highly linear and low noise operation can be possible together in a single chip [4,5,6]. This work reports on the design and fabrication of an ultra-low-noise wideband transimpedance amplifier (TIA) for receiver module.

Due to the large distance between signal emission and reception and considering photodiode sensitivity, a requirement of 100 nA is set for the input noise current of the

TIA with an ultimate bandwidth of 20 GHz. Such low current levels are important to increase the sensitivity of the receiver  $(R_x)$  modules. This translates to an input referred noise current of  $1pA/\sqrt{Hz}$ , which is well below state-of-the-art (SOA), as indicated above.

Such an achievement in InP DHBT based circuit is novel and very appealing, since InP DHBT based circuits have shown immense potential with high RF output power generation along with relatively low noise performance [4,5,6] and high bandwidth. Not only a low noise TIA development would enhance the portfolio of InP DHBT based circuits, but also enable future full MMIC  $T_x/R_x$  module development that are either monolithically grown or hetero-integrated MMIC connected via flip chip or bond-wires. The TIA aims at a flip chip integration in PCB as a proof of concept, success of which will eventually lead us to a fully integrated MMIC.

#### II. TECHNOLOGY

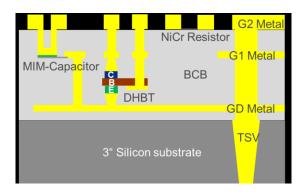

Fig. 1. Simplified layer stack of transferred substrate process

The circuit mentioned in this article is based on the 3-inch FBH transfer-substrate InP-DHBT technology as shown in Fig. 1. In this process, emitter, base and ground layers of the HBT are processed before the complete structure is flipped and bonded on a carrier silicon wafer using the in-house BCB

bonding process. After substrate removal, collector contacts are processed aligned to the emitter contacts. In the first planarization step, the base, collector and emitter are connected to the first metallization layer G1 through a via and a galvanic step. To realize the passives, SiN based Metalinsulator-metal capacitors (MIMs) and NiCr based thin-film resistors (TFRs). Finally, the whole structure is planarized once more with BCB and the second metallization layer is processed. All lithography steps are performed with by a Niko i-line Stepper. The epitaxy is industry-grade DHBT epitaxial layers on 3-inch semi-insulating InP substrates. The base region is a 30 nm thick InGaAs layer optimized for lower transit time through grading the p-doping from the emitter side to the collector side (high to low). The collector epitaxial thickness is 80 nm which allows for a breakdown voltage of 4V.

#### III. CIRCUIT DESIGN

Since a low noise generating circuit is dependent on low noise transistors operating at ultra-low bias points, the design of the TIA is chosen to be simplistic with minimum number of transistors that meets the forward transimpedance requirement. An important aspect is to employ transistors with a high gain at very low bias operating points. This defines the choice of transistor devices. Several topologies exist to design an ultra-low noise TIA, namely, distributed architecture, Cherry-Hooper and feedback based. Since feedback-based TIA can be implemented using small number of transistors, the control of the noise generation depends on the bias of the transistor.

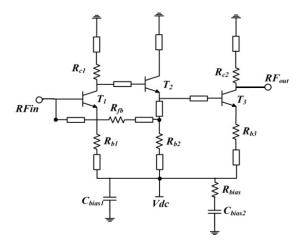

Fig. 2.Simplified circuit schematic

The design used in this work is shown in Fig. 2. The first two transistors form the gain stage of the feedback loop, which acts as the current to voltage converter. The resistive feedback helps to provide a positive feedback loop, thereby increasing the gain performance. The final stage transistor acts as the gain booster with voltage-voltage conversion between its input and output. To reduce the noise generated by the TIA, the bias resistances are chosen such that only 5 mA of collector current flows through the transistor  $T_1$ , much lower than its optimum current of 12 mA ( $I_c$  for highest  $f_{max}$ ).

The feedback resistor  $R_{fb}$  was chosen to be 210  $\Omega$  for optimum noise and gain performance. Resistors  $R_{C1}$ ,  $R_{b1}$  and  $R_{b2}$  set the bias to the transistors  $T_1$  and  $T_2$ . Finally, the bias for transistor  $T_3$  is adjusted by  $R_{b3}$  and  $R_{c2}$  for optimum gain performance. The circuit is biased with only one DC source.

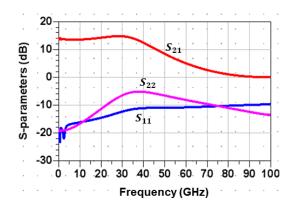

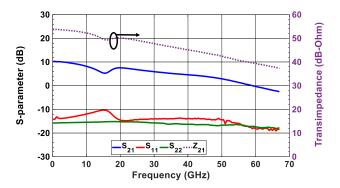

In order to reduce the noise generations, FBH has developed a new process line, which aims at dramatically reducing the base resistance of the transistors, which are currently more than 40  $\Omega$ . According to our estimate, we require a base resistance under 10  $\Omega$  in order to be close to an input referred noise current of 1  $pA/\sqrt{Hz}$ . The final S-parameter simulations are shown in Fig. 3.

Fig. 3. The circuit simulation for S-parameter of the TIA

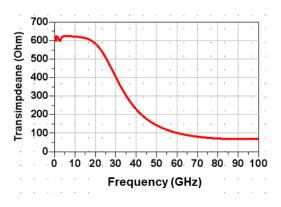

Fig. 4. The circuit simulation for Transimpedance gain (a bias voltage of -1.9 V and 30 mA current was used for simulation)

From Fig. 4 the simulations show that the TIA can offer up to 20 GHz of uniform transimpedance of  $600 \Omega$  with low current noise of  $3 pA/\sqrt{Hz}$  with the currently available InP DHBT process at FBH. With the future technology circuit runs, FBH aims to provide even lower noise performance. The achieved transimpedance is equivalent to >50 dB $\Omega$  up to 20 GHz, which is sufficient of the receiver operation.

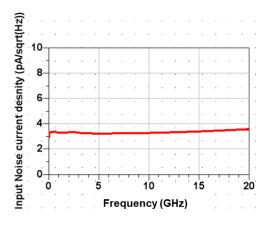

Fig. 5. The circuit simulation for (Input referred noise current (a bias voltage of -1.9 V and 30 mA current was used for simulation)

From Fig. 5, the input referred noise current of the TIA is rather flat across the overall bandwidth of 20 GHz, with a slight increase beyond 10 GHz. This slight increase will be eliminated in a redesign of the TIA, when improved device performance will be available from the FBH InP DHBT process. It is seen from the simulation in Fig. 5 that the input referred noise current requires the new transistors with novel value of base resistance in order to arrive at the envisaged noise performance, which will be done as next steps in the project. The final circuit diagram is given in Fig. 6.

Fig. 6. Picture of the fabricated TIA (extra-large capacitors are added for better DC decoupling) and measures  $1.3 \times 0.7 \text{ mm}^2$

# IV. MEASUREMENTS

The fabricated TIAs small-signal S-parameters have been measured on-wafer and results plotted in Fig. 7. The on-wafer S-parameter measurement has been accomplished using a Keysight PNA-X to 67 GHz with appropriate mTRL calibration down to the probe tips. The measurement provides amplitude and phase results, but only amplitude results are shown in Fig. 7. The forward gain  $S_{21}$  of the TIA exhibits a transimpedance of >52 dB $\Omega$  up to 10 GHz. The reflection parameters are also below 10 dB up to 10 GHz and a return loss around 15 dB up to 5 GHz. The kink visible in the  $S_{11}$  and the  $S_{21}$  is due to capacitance mismatch from simulated values and will be eliminated in the re-design.

Fig. 7. S-parameter measurement of the TIA (1-Gen)

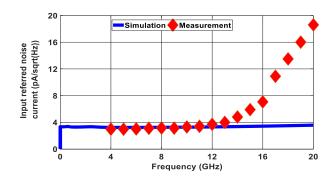

Based on the noise measurement methodology in [8], we have fully characterized the circuit and its noise performance. An input referred noise spectral density equal to 2.95 and 2.98  $pA/\sqrt{Hz}$  at 4 and 5 GHz, respectively, has been measured and determined for this circuit. Fig. 8 shows the measured result vs simulation, the noise performance is approximately  $3 pA/\sqrt{Hz}$  up to 10 GHz, after which it starts to increase. This is mainly because the transimpedance and forward gain  $(S_{21})$  decreases beyond 10 GHz. In future versions, the transimpedance gain of the TIA is targeted to exhibit flat gain beyond 20 GHz, which will enable a flat response of the input referred noise current in the TIA up to 20 GHz. With improvement in transistor technology the absolute value of the noise is targeted to be of the order of  $1 pA/\sqrt{Hz}$ .

Fig. 8. Input referred noise current measurement vs simulation of the TIA (1-Gen)

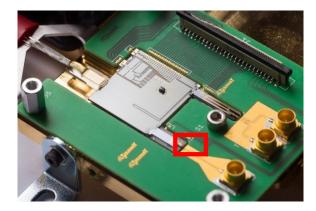

### V. TIA ASSEMBLY FOR RECEIVER SYSTEM

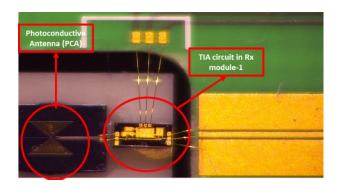

Fig. 9 shows the fully assembled  $R_x$  module containing the TIA, as highlighted by the red box. The TIA is connected after a photoconductive antenna (PCA) via bond wire and the output is fed into a coplanar line for reception. The basic idea is to convert the low magnitude current reception from the PCA and convert it to a voltage signal to the coplanar line. The TIA along with neighboring circuitry in the red box is presented clearly in Fig. 10. The assembly has been performed at PHIX in The Netherlands.

Fig. 9. Full receiver assembly with TIA highlighted (red box)

Fig. 10. TIA connected to the assembly PCB zoomed into the red box of Fig. 9

#### VI. CONCLUSION

In this work, a wideband transimpedance amplifier has been designed, fabricated and measured for the project Teraway which exhibits ultra-low input referred current noise performance of  $3 pA/\sqrt{Hz}$  with a wide bandwidth of beyond 10 GHz and transimpedance gain of more than 50 dB $\Omega$ . Apart from exhibiting the state-of-the-art lowest level of input referred noise current, the circuit achieved significant bandwidth. These results successfully satisfy the first trial specifications of the EU Teraway project.

# ACKNOWLEDGMENT

The authors thank Steffen Schulz for performing the S-parameter measurements. This work was performed within the TERAWAY project that has received funding from the European Union's Horizon 2020 Research and Innovation Programme under G.A No 871668 and it is an initiative of the Photonics Public Private Partnership. Also, the work was partly funded by the German BMBF within the "Forschungsfabrik Mikroelektronik Deutschland (FMD)" framework under ref. 16FMD02.

#### REFERENCES

- [1] I. García López, A. Awny, P. Rito, M. Ko, A. C. Ulusoy, and D. Kissinger, "A 60 GHz bandwidth differential linear TIA in 130 nm sige:C BiCMOS with < 5.5 pA/√Hz," in Proc. IEEE Bipolar/BiCMOS Circuits Technol. Meet. (BCTM), Miami, FL, USA, Oct. 2017, pp. 114–117.</p>

- [2] A. Hiratsuka et al., "A Low Input Referred Noise and Low Crosstalk Noise 25 Gb/s Transimpedance Amplifier with Inductor-Less Bandwidth Compensation," 2018 IEEE Asian Solid-State Circuits Conference (A-SSCC), 2018, pp. 69-72, doi: 10.1109/ASSCC.2018.8579296.

- [3] S. Giannakopoulos, Z. S. He, I. Darwazeh and H. Zirath, "Differential common base TIA with 56 dB Ohm gain and 45 GHz bandwidth in 130 nm SiGe," 2017 IEEE Asia Pacific Microwave Conference (APMC), 2017, pp. 1107-1110, doi: 10.1109/APMC.2017.8251649.

- [4] T. Shivan et al., "A Highly Linear Dual-Stage Amplifier With Beyond 1.75-THz Gain-Bandwidth Product," in IEEE Microwave and Wireless Components Letters, vol. 31, no. 6, pp. 717-720, June 2021, doi: 10.1109/LMWC.2021.3067145.

- [5] T. Shivan et al., "Performance Analysis of a Low-Noise, Highly Linear Distributed Amplifier in 500-nm InP/InGaAs DHBT Technology," in IEEE Transactions on Microwave Theory and Techniques, vol. 67, no. 12, pp. 5139-5147, Dec. 2019, doi: 10.1109/TMTT.2019.2947664.

- [6] T. Shivan et al., "An Ultra-Broadband Low-Noise Distributed Amplifier in InP DHBT Technology," 2018 13th European Microwave Integrated Circuits Conference (EuMIC), 2018, pp. 241-244, doi: 10.23919/EuMIC.2018.8539877.

- [7] T. K. Johansen et al., "Modeling of InP DHBTs in a Transferred-Substrate Technology with Diamond Heat Spreader," 2020 15th European Microwave Integrated Circuits Conference (EuMIC), Utrecht, Netherlands, 2021, pp. 169-172, doi: 10.1109/EuMIC48047.2021.00054.

- [8] H. Hillbrand and P. Russer, "An efficient method for computer aided noise analysis of linear amplifier networks," in *IEEE Transactions on Circuits and Systems*, vol. 23, no. 4, pp. 235-238, April 1976, doi: 10.1109/TCS.1976.1084200.